Obrazový výstup VGA pro DSP za 1 €

Autor: L. Novák, P. Zahradník <zahradni(at)fel.cvut.cz>, Pracoviště: České vysoké učení technické v Praze, FEL, Téma: Digitální zpracování signálu, Vydáno dne: 18. 12. 2008Low-expense Video VGA Output for DSP - Abstract

Low-expense video VGA output for Texas Instruments DSP development kit DSK TMS320C6713 is presented.

Cílem bylo realizovat video výstup s téměř nulovými pořizovacími náklady. Navržený obvod s VGA (Video Graphics Array) výstupem využívá sériového toku dat z rozhraní McBSP (Multichannel Buffered Serial Port) signálového procesoru TMS320C6713. Vnější monostabilní klopné obvody generují synchronizačních pulzy vhodné délky. Generování sériového toku dat probíhá pomocí časovačů a EDMA (Enhanced Direct Memory Access) přenosů. Strojové cykly procesoru jsou plně využity pro vlastní číslicového zpracování signálu.

Návrh a realizace

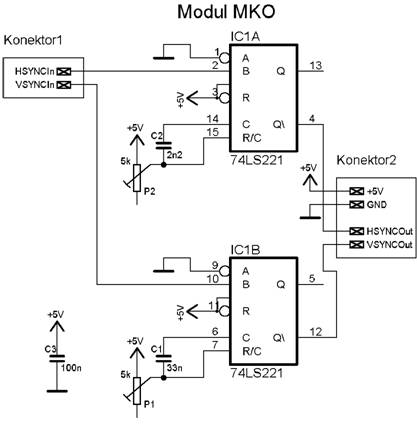

VGA signály jsou generovány pomocí sériového kanálu McBSP0 (signál VIDEO), dvou časovačů Timer 0 (signál VSYNC) a Timer 1 (signál HSYNC) na vývojové desce s DSP C6713. Protože časovače nejsou schopny generovat signály s jinou střídou než 1:1, je jimi řízen dvojitý monostabilní klopný obvod 74LS221, který má nastavené RC konstanty na příslušné doby synchronizačních signálů v log. 0. Zapojení ilustruje obr. 1.

Obr. 1 Blokové schéma VGA s C6713

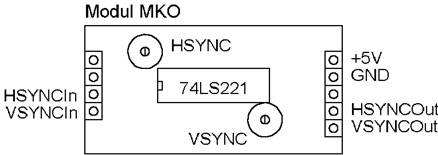

Elektrické zapojení je uvedeno na obr. 2. Je použit dvojitý MKO v integrovaném obvodu 74LS221. Konstrukce a rozvržení modulu je zobrazeno na obr. 3.

Obr. 2 Schéma elektrického zapojení modulu MKO

Obr. 3 Rozvržení modulu MKO

Vertikální synchronizace je generována pomocí časovače Timer 0 a připojeného monostabilního klopného obvodu (viz obr. 1). Timer 0 generuje obdélníkový signál o střídě 1:1 a periodě 16,8 ms. Monostabilní klopný obvod je spouštěn každou náběžnou hranou tohoto obdélníkového signálu, který je na výstupu TOUT0 DSP. Spuštění MKO vyvolá přechod do log. 0 na 64 ms. Tato doba se nastavuje pomocí trimru VSYNC na modulu MKO – třeba zkalibrovat pomocí osciloskopu. Přibližná hodnota odporu odpovídající této době při svitkovém kapacitoru 33 nF je 2,8 kW. (tL=RC ln(2) ).

Horizontální synchronizace je generována pomocí časovače Timer 1 a připojeného monostabilního klopného obvodu (viz obr. 1). Timer 1 generuje obdélníkový signál o střídě 1:1 a periodě 32 ms. Monostabilní klopný obvod je spouštěn každou náběžnou hranou tohoto obdélníkového signálu, který je na výstupu TOUT1 DSP. Spuštění MKO vyvolá přechod do log. 0 na 3,84 ms. Tato doba se nastavuje pomocí trimru HSYNC na modulu MKO – třeba zkalibrovat pomocí osciloskopu. Přibližná hodnota odporu odpovídající této době při svitkovém kapacitoru 2,2 nF je 2,5 kW. (tL=RC ln(2) ).

Obr. 4 Popis EDMA přenosů zajišťujících vysílání VIDEO signálu

V programu je nejprve přenastaven násobící poměr PLL, aby bylo dosaženo pracovního kmitočtu DSP 200 MHz (oproti původním 225 MHz). Je totiž potřeba, aby byl kmitočet fCPU/2 roven celočíselnému násobku žádané vysílací frekvence McBSP tj. zde 4x25 MHz. Dále jsou vhodně nastaveny časovače a poté je spuštěn EDMA přenos edmaInic (obr. 4), který zasynchronizuje vysílání VGA video signálu (VIDEO) se synchronizačními signály HSYNC a VSYNC. Po tomto zasynchronizování a skončení přenosu edmaInic se automaticky spustí edmaActive, který odvysílá VIDEO data (480x800 pixelů na obr. 4 šedě) z pole Buffer. Po skončení edmaActive se ihned automaticky spustí edmaTma, který odvysílá nulové hodnoty VGA vysílání – Front porch, VSYNC pulse a Back porch – řádky 481 až 525 (na obr. 4 modře).

Po skončení tohoto přenosu se opět automaticky „linkováním“ spustí edmaActive, který odvysílá další VIDEO data. Po něm opět automaticky edmaTma atp. Princip a časovací charakteristiky VGA vysílání 640x480 pixelů jsou připomenuty v tab 1. CPU se tedy po počáteční inicializaci již vysílání VGA signálu vůbec neúčastní. VGA signály jsou plně automaticky vysílány pomocí EDMA přenosů, McBSP, časovačů a MKO. Pole Buffer obsahuje 50 16-bit slov (sloupce – 50*16=800 pixelů) a 480 řádků – viz obr. 4. Pouze prvních 40 slov z tohoto pole (indexy 0-39, tj. 640 pixelů) představuje aktivní VIDEO data, zbytek pole (indexy 40-49) je na začátku iniciován nulami a představuje části VGA vysílání FP, HSYNC a BP. DSP/BIOS musí být vypnutý (program nikdy nesmí opustit funkci main() ), protože DSP/BIOS používá časovač Timer 0, ale ten je použitý pro generování VSYNC.

|

Horizontální charakteristiky |

|||||

|

Úsek |

Označení |

Délka v pixelech |

Doba VGA norma [ms] |

Realizovaná doba [ms] |

Relativní chyba [%] |

|

Active video |

A |

640 |

25,42 |

25,6 |

0,71% |

|

Front porch |

B |

16 |

0,636 |

0,64 |

0,63% |

|

HSync pulse |

C |

96 |

3,81 |

3,84 |

0,79% |

|

Back porch |

D |

48 |

1,91 |

1,92 |

0,52% |

|

1 Řádek |

A+B+C+D |

800 |

31,78 |

32 |

0,69% |

|

Vertikální charakteristiky |

|||||

|

Úsek |

Označení |

Délka v řádcích |

Doba VGA norma [ms] |

Realizovaná doba [ms] |

Relativní chyba [%] |

|

Active video |

E |

480 |

15,25 |

15,36 |

0,72% |

|

Front porch |

F |

10 |

0,318 |

0,32 |

0,63% |

|

VSync pulse |

G |

2 |

0,0636 |

0,064 |

0,63% |

|

Back porch |

H |

33 |

1,05 |

1,056 |

0,57% |

|

1 Snímek |

E+F+G+H |

525 |

16,68 tj. 59,94Hz |

16,8 tj. 59,52 Hz |

0,72% |

Tab. 1 Časovací charakteristiky VGA normy pro 640x480 obrazových bodů

Obr. 5 Realizovaný VGA výstup osazený na vývojové desce

Závěr

Byl navržen a realizován modul VGA výstupu, který významně rozšiřuje možnosti výukového přípravku DSK TMS320C6713 pomocí grafického výstupu v reálném čase. Princip výstupu dat plně umožňuje využít výpočetní jádro DSP pro číslicové zpracování signálů. Realizovaný modul spolu s výukovým přípravkem je uveden na obr. 5.

Funkční vzorek vznikl v rámci výzkumného záměru MSM6840770014.

Literatura

[1] www.ti.com

[2] www.tinyvga.com